01

02

03

|

架构方法 |

核心技术 |

性能特征 |

能效 (QPS/W) |

扩展性限制 |

TCO概况 |

主要弱点 |

|

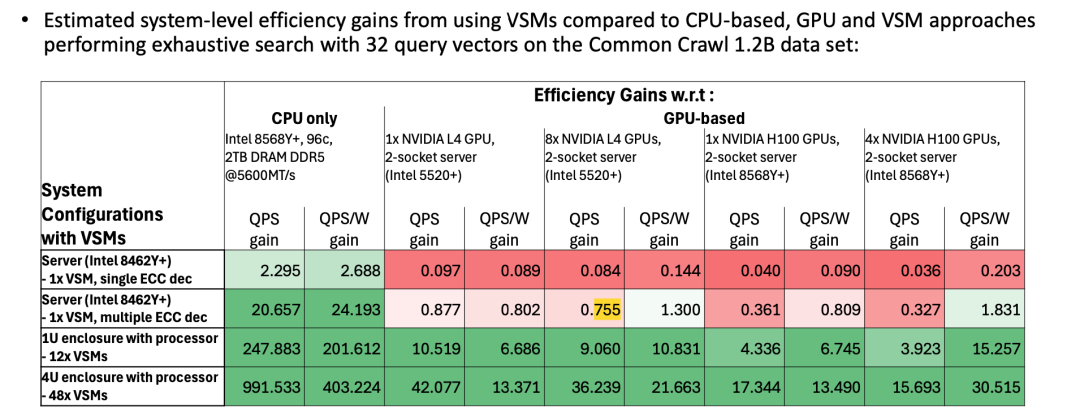

CPU-Only |

SIMD指令集 (如AVX512), 软件库 (如FAISS) |

基准性能,延迟较高 |

低 |

受限于CPU核心数和内存带宽 |

中 |

性能无法满足大规模、低延迟需求 |

|

GPU加速 |

并行计算核心, 专用库 (如NVIDIA cuVS) |

极高性能,低延迟 (数据在VRAM内) |

中 |

受限于VRAM容量和高功耗 |

非常高 |

功耗高,VRAM容量成为新瓶颈,成本昂贵 |

|

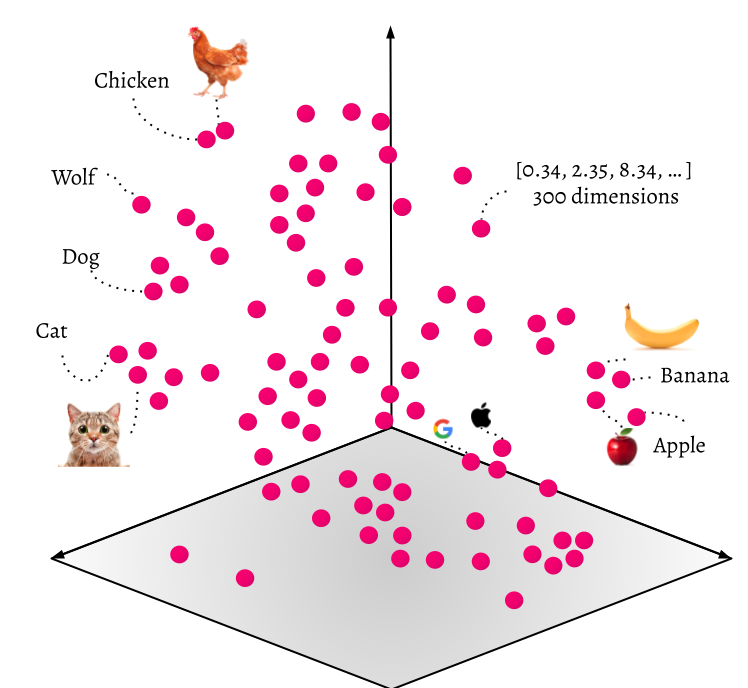

VSM (集成式CSD) |

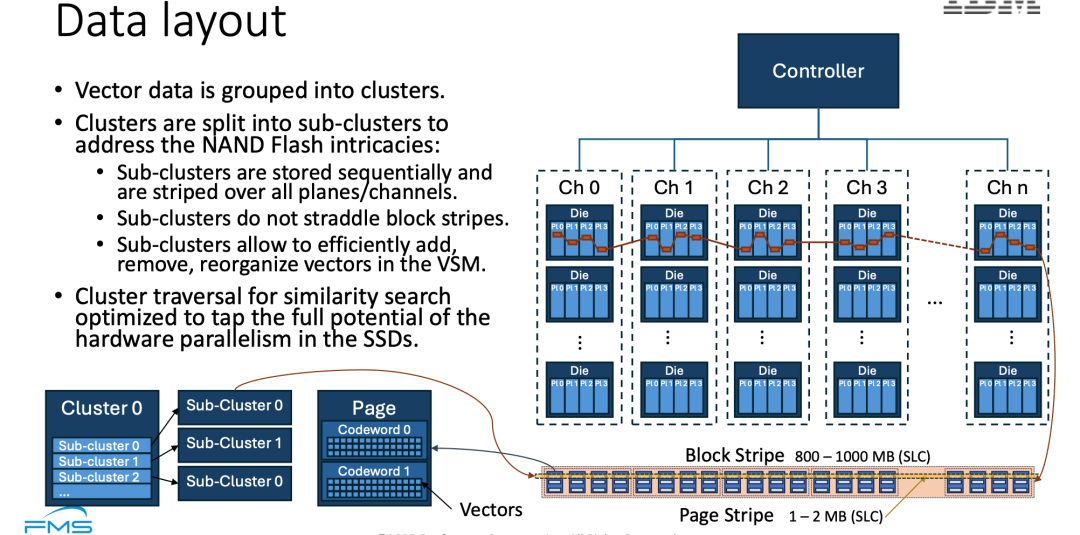

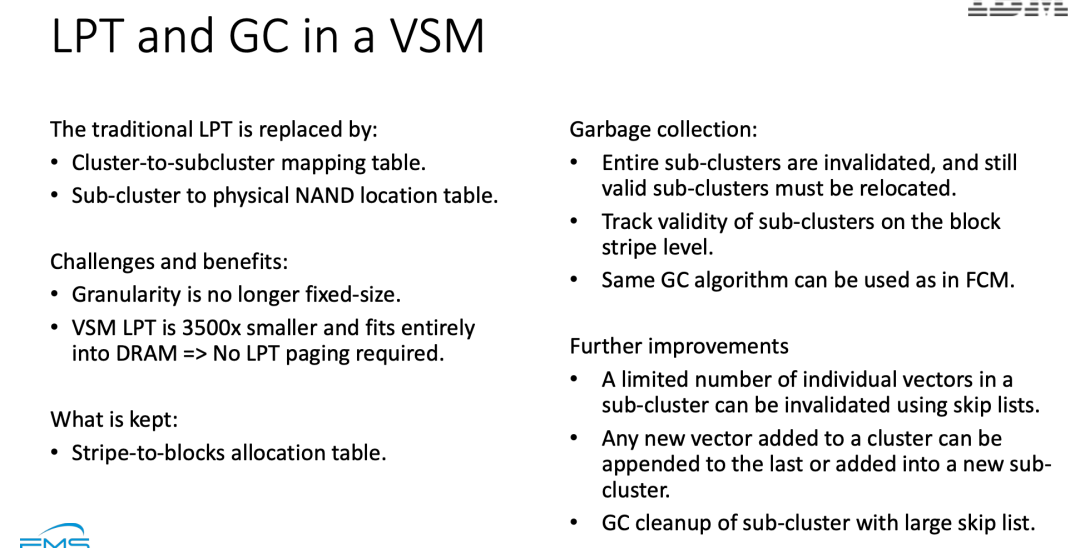

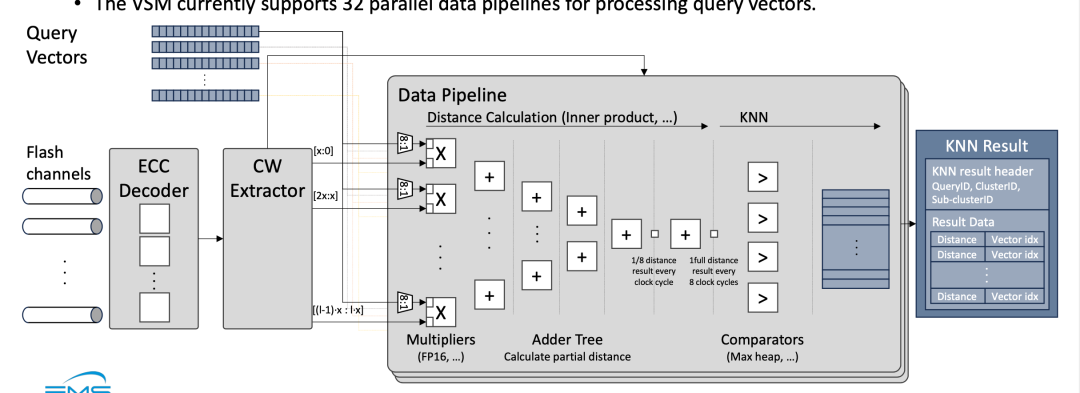

FPGA集成控制器, 专用数据流水线 |

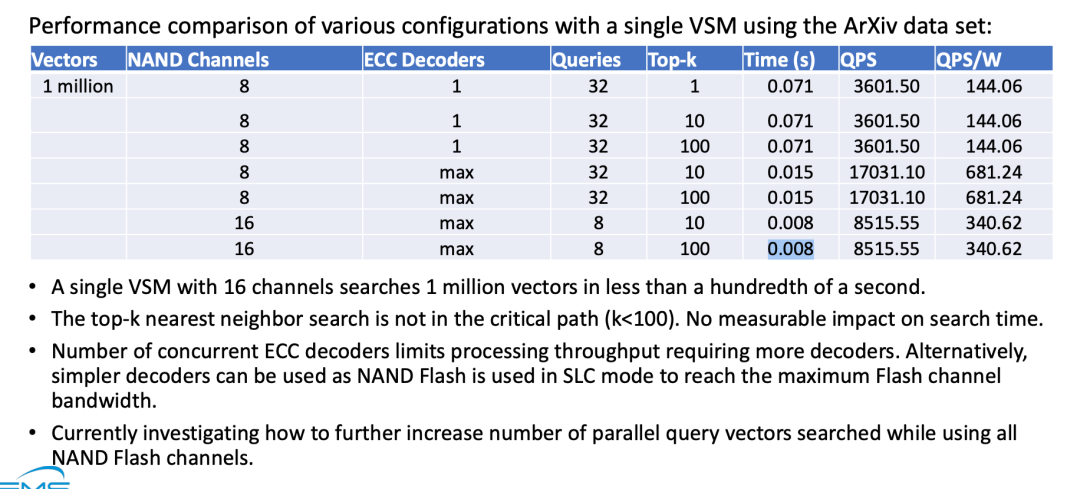

极高性能,低延迟 (数据在闪存) |

非常高 |

可通过增加设备实现近线性扩展 |

低 |

依赖专用硬件,需要新的软件接口和生态系统 |

|

SmartANNS (协作式CSD) |

FPGA/ASIC协处理器, 主机-设备协同 |

高性能,低延迟 |

高 |

类似VSM,但可能受主机调度影响 |

低 |

架构复杂,主机CPU参与度较高 |

|

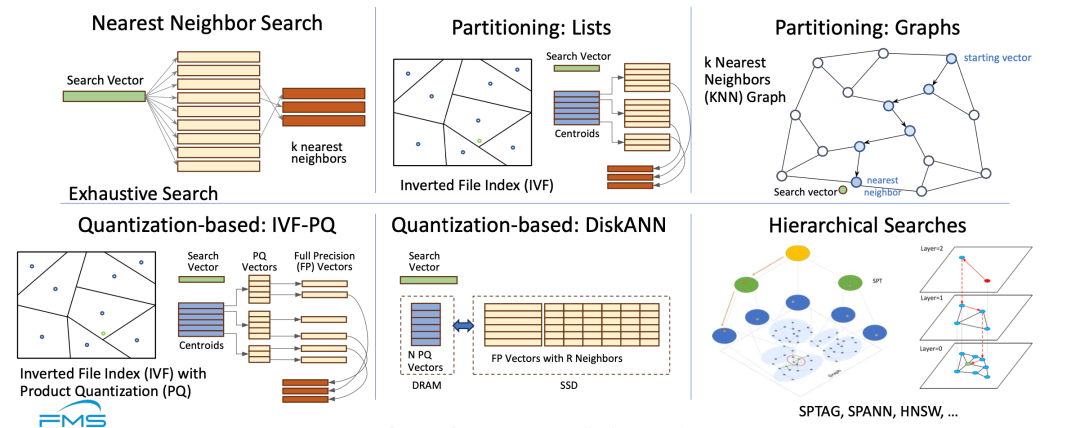

DiskANN (算法优化) |

专为SSD优化的图索引算法 |

性能优于内存算法 (在中等规模),延迟高于内存方案 |

高 (因硬件成本低) |

受限于标准NVMe接口和主机CPU性能 |

非常低 |

性能上限低于专用硬件,无法完全消除主机瓶颈 |

04